DFlipFlop

This block takes the value of the D-input at a specific cycle of the clock, such as the rising edge, when the clear option is off. This value becomes the Q output. At other times, the Q output remains unchanged.

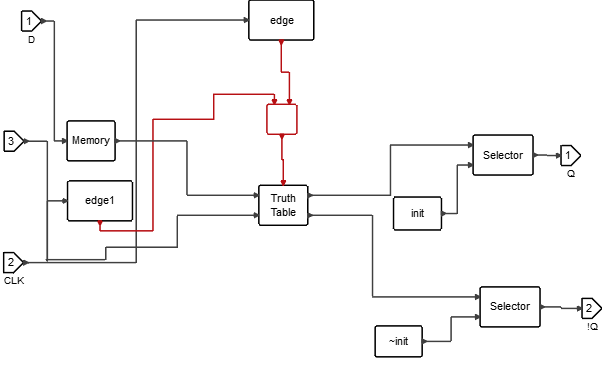

![]()

Library

FlipFlops

Description

The value of port D is copied to the output port Q when the following conditions are satisfied:

a. The rising or falling edge prescribed in the Capture Edge parameter is detected by the input port CLK

b. When the Clear Output Flag parameter is set to "!CLR" and the third input port is non-zero or true.

Alternatively, the parameter is set to "CLR" and the third input port is zero or false.

The truth table for the inputs and outputs are:

D Q !Q

0 0 1

1 1 0

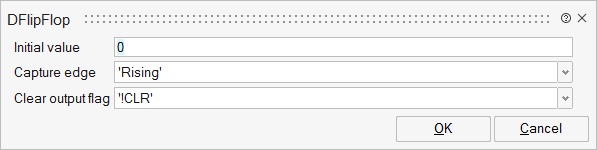

Parameters

| Name | Label | Description | Data Type | Valid Values |

|---|---|---|---|---|

init | Initial value | Initial Value: Output at port Q at initial time | Scalar | |

edge | Capture edge | Capture Edge: Rising or falling edge of port CLK | String | 'Rising' |

edge2 | Clear output flag | Clear Output Flag: This block is enabled when "!CLR" is selected and the third input is non-zero. Alternatively, the block is enabled when "CLR" is selected and the third input is zero. | String | '!CLR' |

Ports

| Name | Type | Description | IO Type | Number |

|---|---|---|---|---|

D | explicit | input | 1 | |

CLK | explicit | input | 2 | |

!CLR | explicit | input | 3 | |

Q | explicit | output | 1 | |

!Q | explicit | output | 2 |