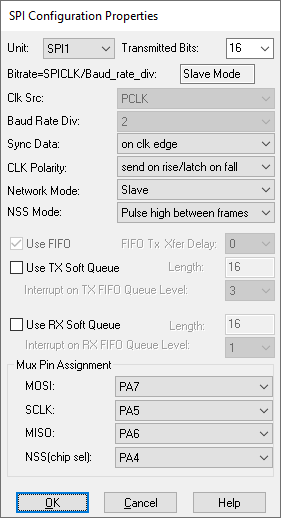

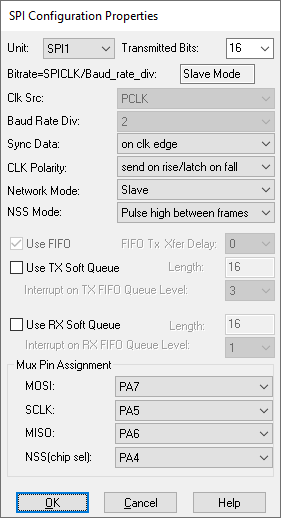

The SPI Config lets you choose the hardware settings for the SPI Read and SPI Write blocks for C2407, Cortex M3, Delfino, F280x, F281X, MSP430, Piccolo, and STM32 targets.

Bit Rate: Sets the bit rate.

Selects the clock for the serial port unit. This parameter is not available for STM32 targets.

ACLK: Auxiliary clock.

Port: Comm

port.

SMCLK: Submain clock.

UCLK: External

clock.

CLK Polarity: Clocks the polarity. You have two choices: Send on rise/Latch on fall and Send on fall/Latch on rise.

Interrupt on RX Fifo Queue Level: Specifies the FIFO level at which an interrupt is generated. A value of n or n-1, where n is the FIFO length, will minimize interrupt occurrences.

Interrupt on TX Fifo Queue Level: Specifies the FIFO level at which an interrupt is generated. Generally, a value of 1 will minimize interrupt occurrence. Note that interrupts are enabled only when the FIFO is filled and additional items have been written to the soft queue.

Length: Specified the length of the software queue. The queue will allow buffering up to the specified number of elements.

Mux Pin Assignment: Sets the external pins used to carry the SPI signals.

Network Mode: Sets the mode to master or slave.

Prescale: Chooses the prescale factor. This parameter is available only for STM32 targets. It is settable only in master mode.

SPIDiv: Specifies the divider for the system clock to set the SPI clock rate. T

STE/NSS Mode: Enables the slave to transmit data.

Sync Data: Synchronizes the data on the clock edge or ½ cycle before clock edge.

Transmitted Bits: Sets the number of bits transmitted per transaction (1-16).

Unit: Specifies the unit number.

Use FIFO: Selects use of the hardware FIFO (if present).

Use RX Soft Queue: Selects use of a software queue. This queue is interrupt driven and will be filled automatically by the Embed driver.

Use TX Soft Queue: Selects use of a software queue. This queue is interrupt driven and will be drained automatically by the Embed driver.